### 性能特点

工作频段: DC - 6 GHz衰减范围: 0.25 - 31.75 dB

IP1dB: 25 dBmIIP3: 43 dBm

• ESD: 500 V HBM

支持串口和并口两种控制方式24-pin 4 mm × 4 mm × 0.75 mmQFN leadless package

## 产品简介

ADIC454LP4是一款频率覆盖DC - 6 GHz 的7位数控衰减器。该产品在整个工作频段的插入损耗小于4 dB, 其基本衰减位为0.25 dB、0.5 dB、1 dB、2 dB、4 dB、8 dB、16 dB,总衰减量为31.75 dB。该衰减器可采用串行/并行信号控制,在整个工作频率范围内具有优良的衰减特性和端口驻波特性。非常适合应用于微波混合集成电路和多芯片模块以及低功耗系统。

# 推荐工作条件

| 参数          | 最小  | 典型  | 最大   |

|-------------|-----|-----|------|

| 偏置电压VDD (V) | 2.3 | 3.3 | 5.5  |

| 电流 (μA)     | -   | 60  | 120  |

| 数字输入高电压(V)  | 1.1 | ı   | 3.6  |

| 数字输入低电压(V)  | 0   | 1   | 0.6  |

| 数字输入电流 (μA) | ı   | ı   | 17.5 |

| 射频输入功率(dBm) | -   | -   | 23   |

| 工作温度 (℃)    | -45 | +25 | +105 |

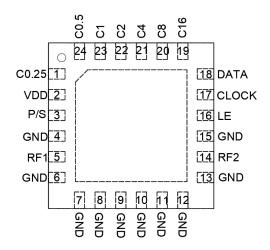

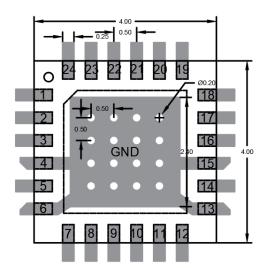

# 引脚定义

服务热线: 028-61399584

俯视透视图

| 引脚编号                            | 符号                                                              | 功能描述                                                    |

|---------------------------------|-----------------------------------------------------------------|---------------------------------------------------------|

| 1, 24, 23,<br>22, 21,<br>20, 19 | D0/C0.25,D1/<br>C0.5,D2/<br>C1,D3/C2,D4/<br>C4,D5/C8,D6/<br>C16 | 0.25 dB,0.5 dB,1<br>dB,2 dB,4 dB,8<br>dB和16 dB衰减控<br>制位 |

| 2                               | VDD                                                             | 电源电压                                                    |

| 3                               | P/S                                                             | 串并模式选择                                                  |

| 5                               | RF1                                                             | 射频输入端口                                                  |

| 14                              | RF2                                                             | 射频输出端口                                                  |

| 16                              | LE                                                              | 串口控制使能端                                                 |

| 17                              | CLK                                                             | 串口控制时钟                                                  |

| 18                              | DATA                                                            | 串口控制数据输入                                                |

| 其它                              | GND                                                             | 地                                                       |

更新日期: 2023-12-01

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

# **电性能表** (VDD = +3.3 V, T= 25 ℃)

| 指标           | 最小值                  | 典型值                      | 最大值      | 单位           | 范围                    |

|--------------|----------------------|--------------------------|----------|--------------|-----------------------|

| 频率范围         | DC                   |                          | 6        | GHz          |                       |

|              |                      | 1.3                      | 2.3      |              | DC - 1 GHz            |

|              |                      | 1.6                      | 2.7      |              | 1 - 2 GHz             |

| 插入损耗         | -                    | 2.4                      | 3.5      | dB           | 2 - 4 GHz             |

|              |                      | 3.1                      | 4.1      |              | 4 - 5 GHz             |

|              |                      | 3.6                      | 4.6      |              | 5 - 6 GHz             |

| □::::+1::=±: |                      | 14                       | -        | d۵           | DC - 4 GHz            |

| 回波损耗         | _                    | 12                       | -        | dB           | 4 - 6 GHz             |

|              | ± (0.2               | ± (0.25+2.5% of Setting) |          | DC - 2.2 GHz |                       |

| 衰减精度         | ± (0.15+2.5% of Sett |                          | Setting) | dB           | 2.2 - 3.0 GHz         |

|              | ± (0.2               | 5+3.5% of                | Setting) |              | 3.0 - 4.0 GHz         |

| IIP3         | 36                   | 48                       |          | dBm          | 0.1 - 3 GHz           |

| IP1dB        | 23                   | 25                       | 31       | dBm          | 0.1 - 3 GHz           |

| 工关时间         |                      | 70                       | -        | ns           | 10%-90% or 90%-10% RF |

| 开关时间<br>     |                      | 150                      | -        | ns           | 50%CTL to 90%/10% RF  |

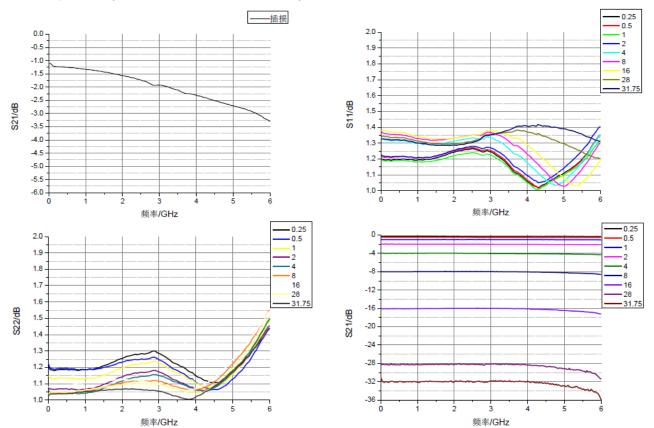

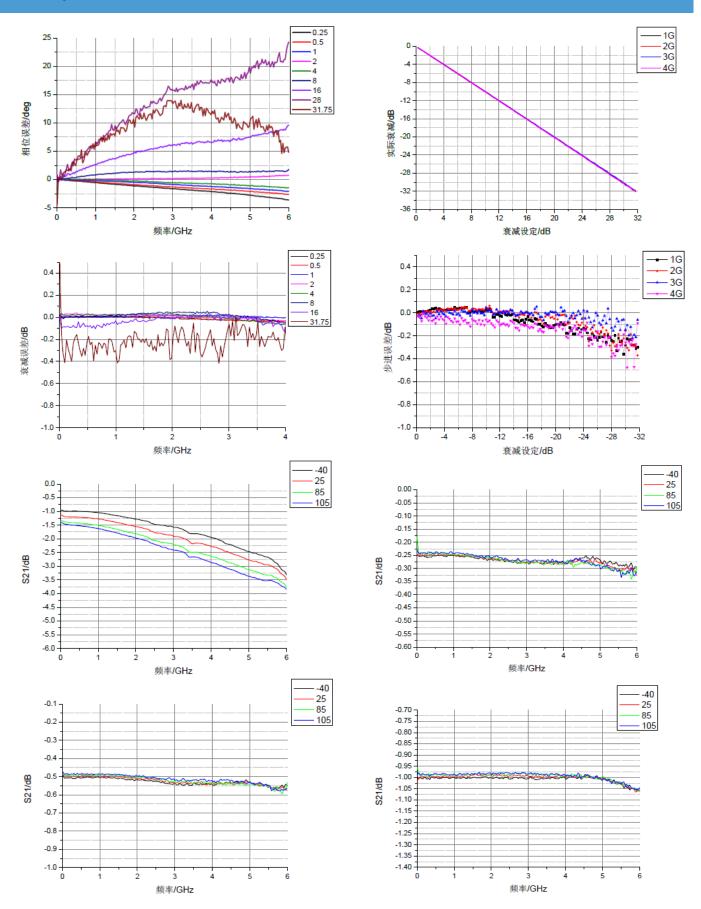

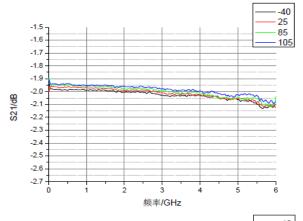

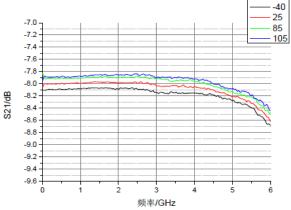

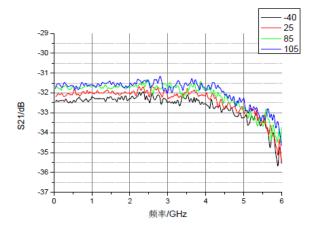

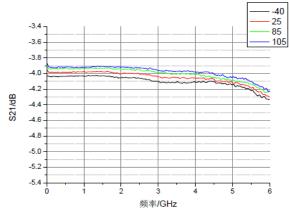

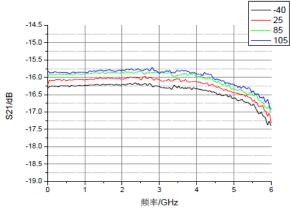

# 典型测试曲线 (VDD=+3.3 V, T= 25 ℃)

# 控制方式

芯片支持串口和并口两种控制方式。P/S 是串并选择的控制位,当P/S = LOW时为并口工作;当P/S = HIGH时为串口工作;

| P/S = LOW  | 并口工作 |

|------------|------|

| P/S = HIGH | 串口工作 |

### 并口控制真值表

|     | 并口控制电压 |    |    |    |      |       | 衰减状态     |

|-----|--------|----|----|----|------|-------|----------|

| C16 | C8     | C4 | C2 | C1 | C0.5 | C0.25 | <b></b>  |

| L   | L      | L  | L  | L  | L    | L     | 参考态      |

| L   | L      | L  | L  | L  | L    | Η     | 0.25 dB  |

| L   | L      | Г  | L  | L  | Н    | L     | 0.5 dB   |

| L   | L      | L  | L  | Н  | L    | L     | 1 dB     |

| L   | L      | L  | Ι  | L  | L    | L     | 2 dB     |

| L   | L      | Η  | L  | L  | L    | L     | 4 dB     |

| L   | Η      | L  | L  | L  | L    | L     | 8 dB     |

| Н   | L      | L  | L  | L  | L    | L     | 16 dB    |

| Н   | Н      | Н  | Н  | Н  | Н    | Н     | 31.75 dB |

#### 并口工作时,分为两种工作状态:

- 1、直接并口工作:直接并口工作时,LE 端口始终接高电平,衰减控制的的改变会直接改变衰减状态。

- 2、带锁定的并口工作: 当衰减控制字改变时, LE 端口需要拉低, 然后 LE 端口需要一个由高 至低的脉冲, 将新的衰减状态更新至芯片内 部, 改变衰减状态。

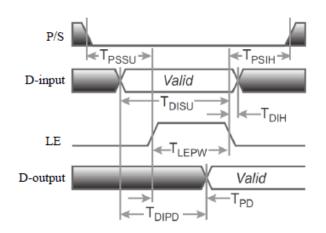

#### 并行工作时序图:

|                   | 并行编码参数                        |     |  |  |  |

|-------------------|-------------------------------|-----|--|--|--|

| 名称                | 定义                            | 最小值 |  |  |  |

| T <sub>PSSU</sub> | 并口工作建立时间(ns)                  | 100 |  |  |  |

| T <sub>PSIH</sub> | 并口工作维持时间(ns)                  | 100 |  |  |  |

| T <sub>DISU</sub> | 并口数据建立时间(ns)                  | 100 |  |  |  |

| T <sub>DIH</sub>  | 并口数据维持时间(ns)                  | 100 |  |  |  |

| T <sub>LEPW</sub> | LE脉宽 (ns)                     | 30  |  |  |  |

| T <sub>DIPD</sub> | 数字寄存器的延迟(内部,<br>直接并口工作模式)(ns) | 5   |  |  |  |

| T <sub>PD</sub>   | 数字寄存器的延迟 (ns)                 | 10  |  |  |  |

#### 串口控制方式真值表

| 衰减控制字 |    |    |    |    |    |    | 衰减状态 |          |

|-------|----|----|----|----|----|----|------|----------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0   | <b></b>  |

| L     | L  | L  | L  | L  | L  | L  | L    | 参考态      |

| L     | L  | L  | L  | L  | L  | L  | Η    | 0.25 dB  |

| L     | L  | L  | L  | L  | L  | Η  | L    | 0.5 dB   |

| L     | L  | L  | L  | L  | Η  | L  | L    | 1 dB     |

| L     | L  | L  | L  | Η  | L  | L  | L    | 2 dB     |

| L     | L  | L  | Ι  | L  | L  | L  | L    | 4 dB     |

| L     | L  | Η  | L  | L  | L  | L  | L    | 8 dB     |

| L     | Н  | L  | L  | L  | L  | L  | L    | 16 dB    |

| Н     | Н  | Н  | Н  | Н  | Н  | Н  | Н    | 31.75 dB |

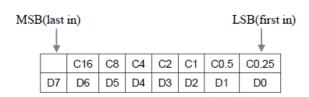

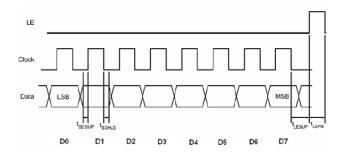

芯片接口是 8 位串行移位寄存输入,再由锁存器缓冲输出。

Data在Clock上升沿触发下串行进入内部移位寄存器。当LE为高时,锁存器直接缓冲输出内部移位寄存器内容。当LE为低时,内部移位寄存器数据被锁存至锁存器。

有效的串行数据应当在LE为低时加载,这样能保持衰减器数据不随串行数据加载而变化。当新数据加载完毕,LE应当翻转到高电平,而后再次回至低电平,由此锁存新数据。

上电态时衰减器被置位为固定的全衰减态,即最大衰减量 31.5 dB 状态,与外接并口信号无关。

#### 串行数据与并行口置位端对应关系

服务热线: 028-61399584

更新日期: 2023-12-01

D7 控制位必须设置为 LOW, 要得到所需的衰减控制字, 需要将衰减量乘以 4, 再将结果转换成二进制。例如, 要得到 1.25 dB 的衰减量, 则

4×12.5=50 50→00110010

串口输入数据应为: 00110010

#### 串口控制时序图

| 串行编码参数             |                             |     |  |  |  |

|--------------------|-----------------------------|-----|--|--|--|

| 名称                 | 定义                          | 最小值 |  |  |  |

| F <sub>clock</sub> | 时钟频率最大值(MHz)                | 10  |  |  |  |

| $T_{clockH}$       | 高电平 (ns)                    | 30  |  |  |  |

| $T_{clockL}$       | 低电平 (ns)                    | 30  |  |  |  |

| T <sub>LESUP</sub> | LE上电间隔(与Data最后一位<br>比较)(ns) | 10  |  |  |  |

| T <sub>LEPW</sub>  | LE脉宽 (ns)                   | 30  |  |  |  |

| T <sub>SDSUP</sub> | 数据置位前置时钟间隔ns)               | 10  |  |  |  |

| T <sub>SDHLD</sub> | 数据保持滞后时钟间隔(ns)              | 10  |  |  |  |

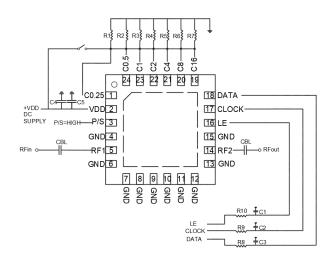

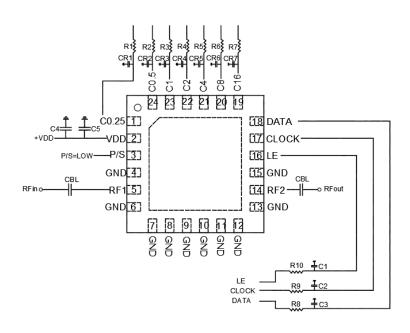

## 应用电路1

注: 1、此示意图用于仅串口控制接法。 C0.25-C16端口电阻用于防止干扰信号, 阻值可适当任选,一般大于 1 K 即可; 2、CBL 为隔直电容,如果射频端口没有 外界直流电位影响,则无须外加隔直电 容;如果有外界直流电位,则工作频率大 于 500 MHz 时,CBL = 68 pF; 3、电源电压范围 2.3~5.5 V。

| 无源器件参数值 |        |        |  |  |  |

|---------|--------|--------|--|--|--|

| 名称      | 名称 描述  |        |  |  |  |

| R1~R7   | 电源下拉电阻 | 10 kΩ  |  |  |  |

| R8~R10  | 输入保护电阻 | 10 kΩ  |  |  |  |

| Свь     | 射频隔直电容 | 68 pF  |  |  |  |

| C1~C4   | 滤波电容   | 100 pF |  |  |  |

| C5      | 滤波电容   | 1 uF   |  |  |  |

6

### 应用电路2

注: 1、此示意图用于串口/并口控制接法。 根据P/S状态选择串并口工作方式;

- 2、CBL为隔直电容,如果射频端口没有外界 直流电位影响,则无需外加隔直电容;如果 有外界直流电位,则工作频率大于 500 MHz 时,CBL = 68 pF;

- 3、电源电压范围 2.3~5.5 V。

| 无源器件参数值         |          |        |  |  |  |

|-----------------|----------|--------|--|--|--|

| 名称              | 描述       | 数值     |  |  |  |

| R1~R7           | 并口信号保护电阻 | 1 kΩ   |  |  |  |

| CR1~CR7         | 滤波电容     | 100 pF |  |  |  |

| R8~R10          | 输入保护电阻   | 10 kΩ  |  |  |  |

| C <sub>BL</sub> | 射频隔直电容   | 68 pF  |  |  |  |

| C1~C4           | 滤波电容     | 100 pF |  |  |  |

| C5              | 滤波电容     | 1 uF   |  |  |  |

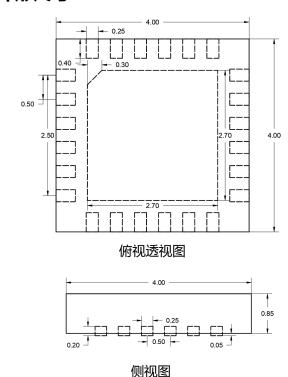

# 外形尺寸

单位: mm

# 建议引脚PCB

服务热线: 028-61399584

更新日期: 2023-12-01