## 性能特点

● 频率覆盖范围:125 MHz 至 4200 MHz

● 基波輸出: 2000 MHz 至 4200 MHz

● 可编程的分频输出: 1/2/4/8/16

• 整数和小数 N 分频频率合成器

• 具有低相位噪声的 VCO

• 典型抖动: < 0.4 ps rms

● 基波噪声: -76 至 -81 dBc/Hz @10 kHz;

-120 至 -127 dBc/Hz @1 MHz

● 电源: 3.0 V 至 3.6 V

可编程双模预分频器: 4/5或8/9

• 三线式串行接口

• RF输出静音功能

• 可编程的输出功率

• 模拟和数字锁定检测

• 工作温度: -45 ℃ 至 85 ℃

# 产品简介

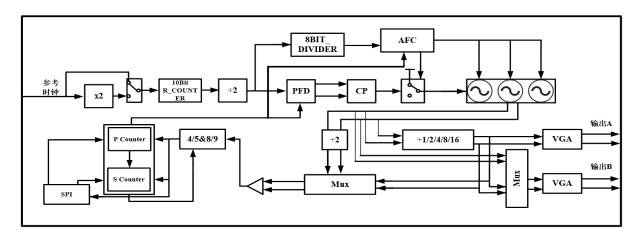

ADIC100LP5结合外部环路滤波器和外部 基准频率使用时,可实现小数N分频或整数N 分频锁相环(PLL)频率综合器。

ADIC100LP5具有一个集成压控振荡器 (VCO), 其基波输出频率范围为2000 MHz 至4200 MHz。此外,利用 1/2/4/8/16 分频电路,用户可以产生低至125 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

所有片内寄存器均通过简单的三线式串行接口进行控制。该器件采用3.0 V-3.6 V电源供电,不用时可以关断。

32 Pin 5×5 mm QFN

## 产品应用

- 无线基础设施(W-CDMA、TD-SCDMA、WiMAX、GSM、PCS、DCS、DECT)

- 测试设备

- 无线局域网 (LAN) 、有线电视设备

- 时钟产生

## 极限参数

| 存储温度 | -55 ℃ ~ 150 ℃  |

|------|----------------|

| 使用温度 | -45 °C ~ 85 °C |

关注公众号

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

# 电性能表

| 参数                                                                                                                             | 最小值         | 典型值                                                        | 最大值                            | 单位                                                                     | 条件/注释                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| REF <sub>IN</sub> 特性<br>输入频率<br>输入灵敏度<br>输入电容<br>输入电流<br><b>鉴相器</b>                                                            | 10<br>2.5   | 10                                                         | 100<br>AV <sub>DD</sub><br>±60 | MHz<br>V p-p<br>pF<br>µA                                               | 如果f< 10 MHz,确保压摆率大于<br>21V/μs<br>AV <sub>DD</sub> /2偏置<br>为保证低至2000 MHz频率输                                                       |

| 鉴相器频率                                                                                                                          |             | 4                                                          | 80                             | MHz                                                                    | 出,推荐使用4 MHz鉴相。                                                                                                                   |

| 电荷泵 I <sub>CP</sub> 吸/源电流 高值 低值 吸电流与源电流匹配 I <sub>CP</sub> 与V <sub>CP</sub> I <sub>CP</sub> 与温度                                 |             | 5<br>0.312<br>1<br>1.5<br>2                                |                                | mA<br>mA<br>%<br>%                                                     | 0.5 V ≤ VCP≤ 2.5 V<br>0.5 V ≤ VCP≤ 2.5 V<br>V <sub>CP</sub> = 2.0 V                                                              |

| <b>逻辑输入</b><br>输入高电压V <sub>INH</sub><br>输入低电压V <sub>INL</sub><br>输入电流I <sub>INH</sub> /I <sub>INL</sub><br>输入电容C <sub>IN</sub> | 1.5         | 3.0                                                        | 0.6<br>±1                      | V<br>V<br>µA<br>pF                                                     |                                                                                                                                  |

| 逻辑输出<br>输出高电压VoH<br>输出高电流IoH<br>输出低电压VoL                                                                                       | DVDD -      | 0.4                                                        | 500<br>0.4                     | V<br>mA<br>V                                                           | 选择CMOS输出<br>I <sub>OL</sub> = 500 µA                                                                                             |

| 电源<br>AV <sub>DD</sub><br>DV <sub>DD</sub> , V <sub>VCO</sub> , SD <sub>VDD</sub> , V <sub>P</sub>                             | 3.0         | 3.3<br>AV <sub>DD</sub>                                    | 3.6                            | V                                                                      | 这些电压必须等于A <sub>VDD</sub>                                                                                                         |

| DI <sub>DD</sub> + AI <sub>DD</sub><br>输出分频器<br>I <sub>VCO</sub>                                                               |             | 21<br>6 to 24<br>65                                        | 27<br>75                       | mA<br>mA<br>mA                                                         | 每个二分频输出消耗6 mA<br>RF输出级可编程                                                                                                        |

| IRFOUT  RF输出特性 最大VCO输出频率 最小VCO输出频率 使用分频器时最小VCO输出频率 VCO灵敏度 最小VCO调谐电压 最大VCO调谐电压                                                  | 2000<br>125 | 33<br>0.5<br>2.5                                           | 4200                           | MHz<br>MHz<br>MHz<br>MHz/V<br>V                                        | 2000 MHz基波输出,选择16分<br>频                                                                                                          |

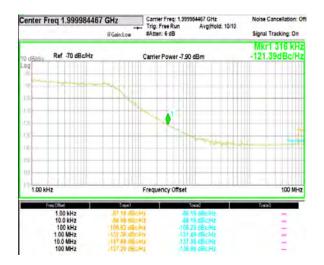

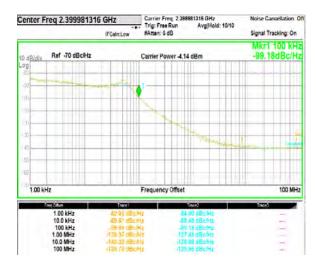

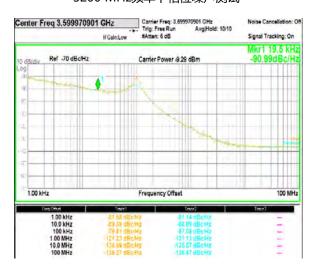

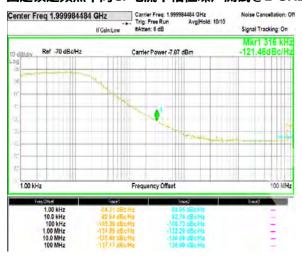

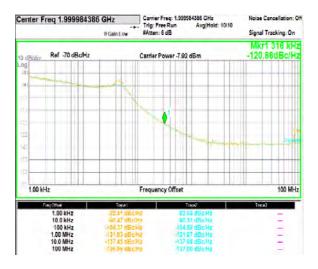

| <b>噪声特性</b> PLL相位噪声性能  PFD频率引起的杂散信号 使能RF静音时的信号电平                                                                               |             | -88<br>-108<br>-131.49<br>-89<br>-90<br>-127<br>-70<br>-40 |                                | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc<br>dBc | 10 KHz偏移、2000MHz载波<br>100 KHz偏移、2000MHz载波<br>1 MHz偏移、2000MHz载波<br>10 KHz偏移、2400MHz载波<br>100 KHz偏移、2400MHz载波<br>1 MHz偏移、2400MHz载波 |

服务热线: 028-61399584

## 简化原理框图

## 典型工作特性

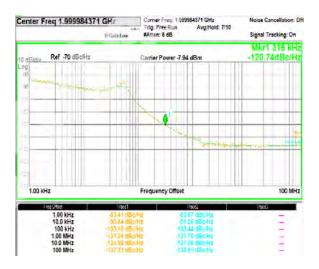

2000 MHz频率下相位噪声测试

2400 MHz频率下相位噪声测试

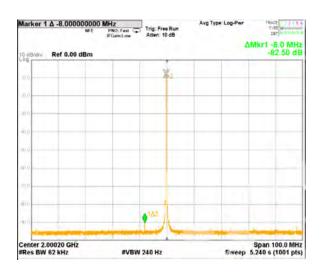

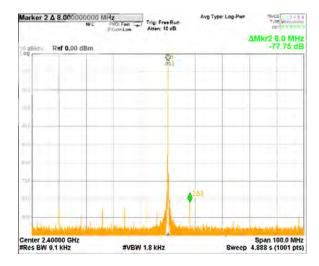

8 MHz鉴相频率下参考杂散 (整数分频) 2000 MHz

8 MHz鉴相频率下参考杂散 (整数分频) 2400 MHz

## 典型工作特性

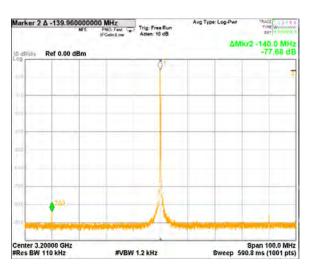

3200 MHz频率下相位噪声测试

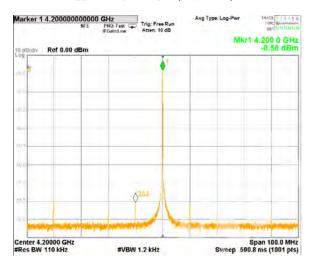

3600 MHz频率下相位噪声测试

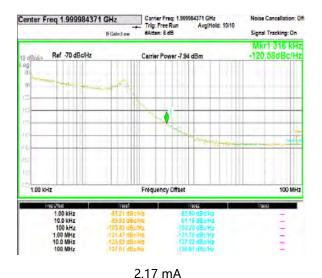

## 固定锁定频点不同CP电流下相位噪声测试@2 GHz

0.31 mA 0.62 mA

服务热线: 028-61399584

70 MHz鉴相频率下参考杂散 (整数分频) 3200 MHz

10 MHz鉴相频率下参考杂散 (整数分频) 4200 MHz

## 典型工作特性

0.93 mA

1.55 mA

1.24 mA

1.86 mA

2.48 mA

服务热线: 028-61399584

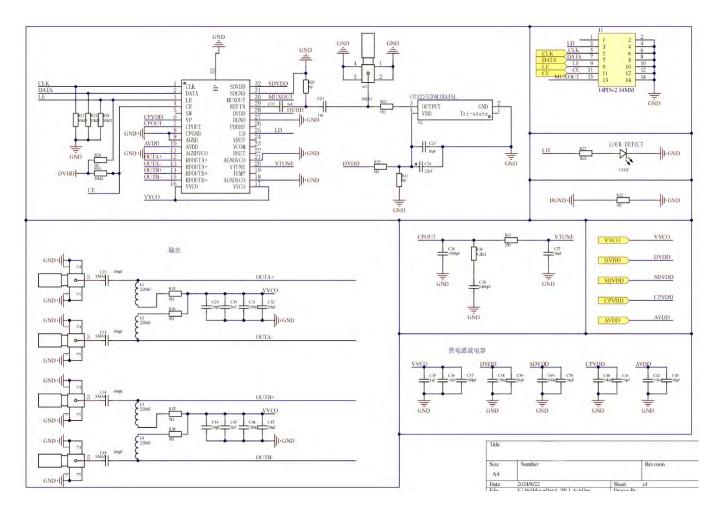

## 参考电路设计

## ADIC100LP5原理图

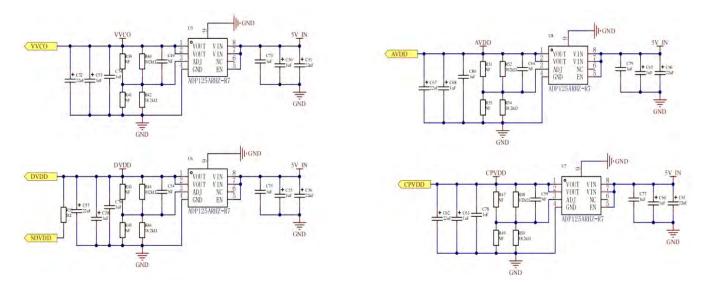

## ADIC100LP5供电原理图

## 整数/小数N分频频率综合器, 125 - 4200 MHz

ADIC100LP5

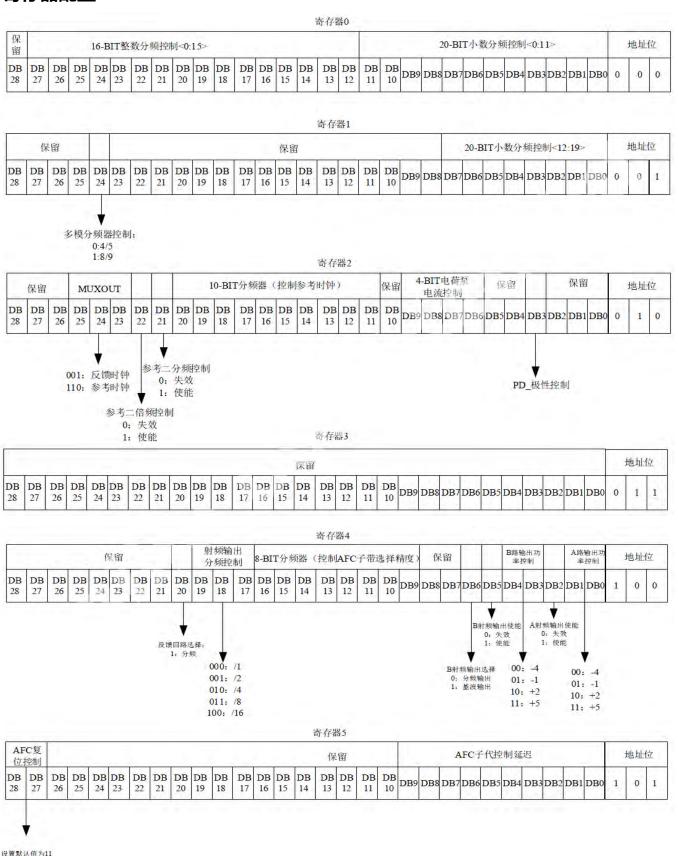

## 寄存器配置

ADIC100LP5

## 寄存器配置

## 寄存器0

## • 控制位

当位[C3:C1]设置为0、0、0时,可对寄存器0进行编程。

## • 16位INT值

寄存器0的16位可设置INT值,它决定反馈分频系数的整数部分,用于公式1计算输出频率。对于4/5预分频器,可以设置从16到65,535的所有整数值。对于8/9预分频器,最小整数值为64,对于ADIC100LP5低于4 GHz可以采用8/9预分频器完成全频带锁定。

## • 20位FRAC值

寄存器0包含20位FRAC的低12位,用于设置Σ-Δ调制器小数输入的分子。它与INT一起决定频率源输出的频率。在使用FRAC功能时,使用4 MHz或者8 MHz的鉴相时钟。

#### 寄存器1

## • 控制位

当位[C3:C1]设置为0、0、1时,可对寄存器1进行编程。

#### • 预分频器值

双模预分频器 (P/P+1) 与INT、FRAC一起,决定从VCO输出到PFD输入的整体分频比。预分频器工作在CML电平,从VCO输出获得时钟,并针对分频器进行分频。它基于同步4/5内核。

#### 20位FRAC值

寄存器1包含20位FRAC的高8位,用于设置Σ-Δ调制器小数输入的分子。它与INT一起决定频率源输出的频率。在使用FRAC功能时,使用4 MHz或者8 MHz的鉴相时钟。

## 寄存器2

## • 控制位

当位[C3:C1]设置为0、1、0时,可对寄存器2进行编程。

#### MUXOUT

片内多路复用器由位[DB25:DB23]控制(参见寄存器2)

## 参考倍频器

当DB22设置为0时,倍频器禁用, REFIN信号直接接入10-bit的R分频器。当此位设置为1时, REFIN频率加倍,然后接入10-bit的R分频器。倍频器禁用时, REFIN下降沿是小数频率合成器的PFD输入端的有效沿。倍频器使能时,REFIN的上升沿和下降沿均是PFD输入端的有效沿。

当使能倍频器,带内相位噪声性能对REFIN占空比敏感。对于45%至55%范围之外的REFIN占空比,相位噪声性能下降可能多达5dB。在最低噪声模式下,并且倍频器禁用时,相位噪声性能对REFIN占空比不敏感。

## RDIV2

当DB21设置为1时,R分频器与PFD之间将插入一个二分频触发器,以扩大REFIN最大输入速率。此功能使得PFD输入端信号占空比为50。

## • 10位R分频器

利用10位R分频器,可以细分输入基准频率(REFIN)以产生PFD的基准时钟。分频比可以为2至1023。

#### • 电荷泵电流设置

位[DB9:DB9]用于设置电荷泵的电流。基础电流为 0.31 mA, 最大输出5 mA。

#### 鉴相器极性

DB3设置鉴相器极性。如果使用无源环路滤波器或同相有源环路滤波器,则应将其设置为1。如果使用反相有源滤波器,则应将其设置为0。

ADIC100LP5

## 寄存器配置

## 寄存器3

## • 控制位

当位[C3:C1]设置为0、1、1时,可对寄存器3进行编程。

## 寄存器4

## • 控制位

当位[C3:C1]设置为1、0、0时,可对寄存器4进行编程。

## • 反馈选择

DB20选择从VCO输出到N分频器的反馈。设置为1时,信号直接从VCO经过内部二分频器获得。

#### • 分频器选择

位[DB19:DB17]选择输出分频器的值(参见寄存器4)。

#### • 频段选择时钟分频器值

寄存器4的[DB16:DB9]设置频段选择逻辑时钟输入的分频器。R分频器的输出默认用作频段选择逻辑时钟,但如果此值太大(>125 kHz),则可以启用一个分频器,以将R分频器输出细分为较小的值。

## • 辅助输出选择

DB6设置辅助RF输出。可以选择RF分频器的输出或VCO基频。

#### • 辅助输出使能

根据所选择的值,DB5使能或禁用辅助RF输出。

#### • 辅助输出功率

位[DB4:DB3]设置辅助RF输出功率水平的值。

## • RF输出使能

根据所选择的值,DB2使能或禁用主RF输出。

#### • 输出功率

位[DB1:DB0]设置主RF输出功率水平的值。

## 寄存器5

#### • 控制位

当位[C3:C1]设置为1、0、1时,可对寄存器5进行编程。

## • AFC子代控制延迟

位[DB9:DB0]设置子代跳变的间隔时间,当锁定频率低于2.9 GHz,将AFC设置为1000(十进制)。

## • AFC复位控制

默认设置11

#### 输出频率计算公式1:

RFOUT = 2× (INT×Fpfd+Fpfd/2<sup>20</sup>×Frac) INT为16bit整数控制; Frac为20bit小数控制; Fpfd为鉴频鉴相时钟

Fpfd=Fref/R×D×1/DIV

Fref为参考时钟, R为寄存器2中的10bit分频器, 最小值为2.D和DIV为寄存器2中参考二倍频和二分频。当D和DIV失效时, Fpfd = Fref/R

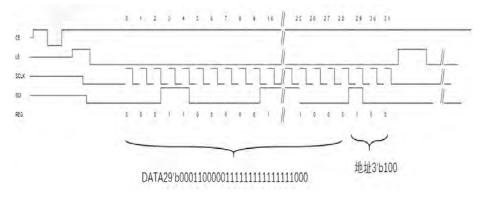

## 时序配置说明

- 1.每组寄存器共计32位,包括 a<2:0>3位地址位,d<28:0>29位 数据位;

- 2.SCLK上升沿,读取DATA数据; 3.每个寄存器写入完毕后,LE拉高 再拉低进行下个寄存器写入;

- 4.CE拉低再拉高, 进入写入操作。

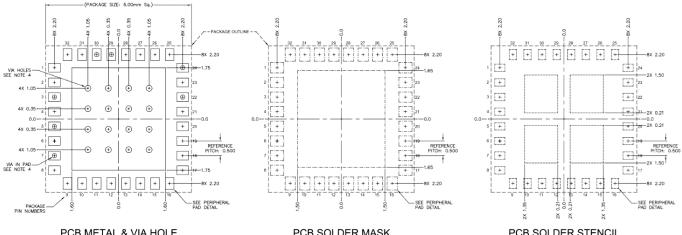

## PCB参考设计

PCB METAL & VIA HOLE

PCB SOLDER MASK TOP (X-Ray) VIEW

服务热线: 028-61399584

PCB SOLDER STENCIL TOP (X-Ray) VIEW

更新日期: 2024-12-01

- GENERAL NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCES CONFORM TO ASME Y14.5M-1994.

(UNLESS OTHERWISE SPECIFIED THE FOLLOWING VALUES APPLY)

DECIMAL TOLERANCE:

X.X (1 PLC) ± 0.1mm

X.XXX (2 PLC) ± 0.05mm

X.XXX (3 PLC) ± 0.025mm

3. UNLESS SPECIFIED DIMENSIONS ARE SYMMETRICAL ABOUT CENTER LINES.

#### RECOMMENDED FOOTPRINT NOTES:

- Sb. ALL GROUND PADDLE FEATURES ARE SOLDER MASK DEFINED.

6. SOLDER STENCIL, APERTURE FEATURES:

6a. SOLDER STENCIL APERTURE OPENINGS ARE SMALLER THEN PERIPHERAL PCB METAL PADS.

6b. RECOMMENDED SOLDER STENCIL APERTURE ARRAY TO TARGET APPROXIMATELY

50 80% COVERAGE OF SOLDER MASK OPENINGS, EXCEPT AS NOTED.

7. RECOMMENDED SOLDER STENCIL THICKNESS: 5. Somils (C.127mm).

8. PCB ACAD AND GERBER FILES AVAILABLE UPON REQUEST.

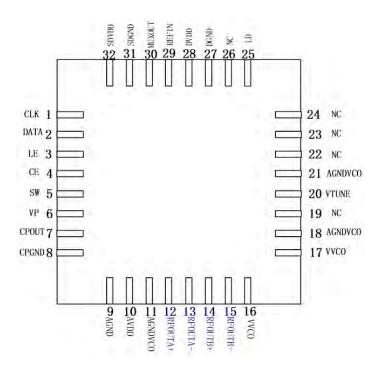

## 引脚定义

# 整数/小数N分频频率综合器, 125 - 4200 MHz

ADIC100LP5 V0

# 引脚功能描述

| 引脚编号           | 符号      | 功能描述                                                                                   |

|----------------|---------|----------------------------------------------------------------------------------------|

| 1              | CLK     | 串行时钟输入。数据在CLK上升沿时逐个输入32位移位寄存器。此输入为高阻抗<br>CMOS输入。                                       |

| 2              | DATA    | 串行数据输入。串行数据以MSB优先方式加载,三个LSB用作控制位。此输入为高阻抗CMOS输入。                                        |

| 3              | LE      | 加载使能,CMOS输入。当LE变为高电平时,存储在移位寄存器中的数据载入三个LSB<br>所选择的寄存器。                                  |

| 4              | CE      | 芯片使能。此引脚的逻辑低电平将关断器件,并使电荷泵进入三态模式。根据关断位的状态不同,此引脚逻辑高电平将使器件上电。                             |

| 5              | SW      | 快速锁定开关。使用快速锁定模式时,必须将环路滤波器与此引脚相连。                                                       |

| 6              | VP      | 电荷泵电源。此引脚须等于AVDD。至地层的去耦电容应尽可能靠近此引脚。                                                    |

| 7              | CPOUT   | 电荷泵输出。使能时,此引脚向外部环路滤波器提供±ICP。环路滤波器的输出连到<br>VTUNE,以驱动内部VCO。                              |

| 8              | CPGND   | 电荷泵接地。这是CPOUT的接地回路引脚。                                                                  |

| 9              | AGND    | 模拟地。                                                                                   |

| 10             | AVDD    | 模拟电源。范围为3.0 V至3.6 V。至模拟地层的去耦电容应尽可能靠近此引脚。                                               |

| 11             | AGNDVCO | VCO模拟地。这些是VCO的接地回路引脚。                                                                  |

| 12             | RFOUTA+ | VCO输出。输出电平可编程。提供VCO基波输出或分频输出。                                                          |

| 13             | RFOUTA- | 互补VCO输出。输出电平可编程。提供VCO基波输出或分频输出。                                                        |

| 14             | RFOUTB+ | 辅助VCO输出。输出电平可编程。提供VCO基波输出或分频输出。                                                        |

| 15             | RFOUTB- | 互补辅助VCO输出。输出电平可编程。提供VCO基波输出或分频输出。                                                      |

| 16             | VVCO    | VCO电源。范围为3.0 V至3.6 V。至模拟地层的去耦电容应尽可能靠近这些引脚。                                             |

| 17             | VVCO    | VCO电源。范围为3.0 V至3.6 V。至模拟地层的去耦电容应尽可能靠近这些引脚。                                             |

| 18             | AGNDVCO | VCO模拟地。这些是VCO的接地回路引脚。                                                                  |

| 19、22、23、24、26 | N/C     |                                                                                        |

| 20             | VTUNE   | VCO的控制输入。此电压决定输出频率,从对CPOUT输出电压的滤波而获得。                                                  |

| 21             | AGNDVCO | VCO模拟地。这些是VCO的接地回路引脚。                                                                  |

| 25             | LD      | 锁定检测输出引脚。此引脚输出逻辑高电平时表示PLL锁定。逻辑低电平输出表示PLL失锁。                                            |

| 27             | DGND    | 数字地。                                                                                   |

| 28             | DVDD    | 数字电源。范围为3.0 V至3.6 V。                                                                   |

| 29             | REFIN   | 基准输入。这是一个CMOS输入,标称阈值为V <sub>DD</sub> /2,并具有100 kΩ的直流等效输入电阻。此输入可以采用TTL或CMOS品振驱动,或者交流耦合。 |

| 30             | MUXOUT  | 多路复用器输出。此多路复用器输出允许从外部访问锁定检测、经过缩放的RF或基准频率。                                              |

| 31             | SDGND   | 数字Σ-Δ调制器接地。                                                                            |

| 32             | SDVDD   | 数字Σ-Δ调制器的电源引脚。范围为3.0 V至3.6 V。                                                          |

服务热线: 028-61399584

# 整数/小数N分频频率综合器, 125 - 4200 MHz

ADIC100LP5 Vo

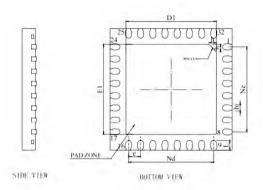

# 外形尺寸

服务热线: 028-61399584

| SYMBOL | ALITHMALEN |        |        |  |  |  |

|--------|------------|--------|--------|--|--|--|

|        | MY         | NOIL   | 9.58   |  |  |  |

| ٨      | 0.70       | 0.75   | 0/80   |  |  |  |

| - NI   |            | 0.02   | 0.05   |  |  |  |

| eb     | 01,20      | 0.25   | 0.30   |  |  |  |

| 41     | 0.203RE)   |        |        |  |  |  |

| Ď      | 1,90       | 5: 00  | etc 10 |  |  |  |

| 194    | 8, 60      | 3.78   | 3.80   |  |  |  |

| - é    | 0, 50RSc   |        |        |  |  |  |

| he     | 3 50BSC    |        |        |  |  |  |

| - Sd.  | 8, 50RSC   |        |        |  |  |  |

| 6      | 4. 90      | 5.00   | ā; 10  |  |  |  |

| FI     | 3, 60      | 3.70   | 3,80   |  |  |  |

| 11     | 0.35       | 0.40   | 0.46   |  |  |  |

| h.     | 0.25       | 9, 30. | 0.35   |  |  |  |